SystemRDL语法、IC验证资料与专业社区全解析

在集成电路(IC)设计,特别是复杂片上系统(SoC)的开发流程中,寄存器抽象层的高效描述与功能验证是确保芯片成功的关键环节。本文将围绕SystemRDL规范示例、IC验证技术资料以及相关的专业工程师社区,为微电子与电子电路领域的从业者提供一个综合性的知识导航。

一、SystemRDL:寄存器描述的标准化语言

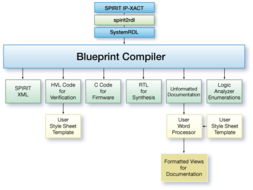

SystemRDL(System Register Description Language)是一种专门用于描述数字系统中寄存器和内存映射的硬件描述语言。它超越了传统的IP-XACT或自定义表格,提供了一种机器可读且功能丰富的标准方式。

语法示例与核心概念:

一个简单的SystemRDL定义可能如下所示:`systemrdl

addrmap top {

reg myreg {

field {} data @0x0;

};

};`

此例定义了一个名为“top”的地址映射,其中包含一个寄存器“myreg”,该寄存器在偏移地址0x0处有一个名为“data”的字段。SystemRDL的强大之处在于其能精确定义字段的访问权限(如读/写、只读)、硬件行为(如写后清除、计数器)、复位值以及复杂的层次化地址空间结构。掌握其语法对于生成精确的寄存器传输级(RTL)代码、验证测试平台、C/C++头文件以及文档至关重要。

二、IC验证:确保设计正确的基石

IC验证是使用仿真、形式验证、硬件仿真等多种方法,确保RTL设计符合功能规格和性能要求的过程。相关技术资料涵盖极广:

- 方法论与语言:以通用验证方法学(UVM)为主导,结合SystemVerilog语言,构建标准化、可重用的验证平台。资料包括UVM框架详解、测试用例(Testbench)构建、序列(Sequence)、驱动器(Driver)、监视器(Monitor)和记分板(Scoreboard)的设计。

- 验证IP(VIP):针对标准接口(如AMBA AXI、USB、PCIe)的预验证组件,能极大加速验证进程。学习如何集成和使用VIP是重要课题。

- 模拟与调试:涉及主流仿真工具(如Synopsys VCS, Cadence Xcelium, Siemens EDA Questa)的使用技巧、覆盖率(代码覆盖率、功能覆盖率)收集与分析、以及高效的调试技术。

- 前沿技术:形式验证、便携式激励(PSS)、硬件辅助验证(如FPGA原型验证、硬件仿真器)的相关资料也日益重要。

三、专业工程师社区与论坛:知识分享与问题求解的沃土

电子工程师的成长离不开同行交流。以下社区是获取资料、探讨难题的宝贵平台:

- EETOP(创芯网论坛):国内最具影响力的集成电路专业社区之一。其板块全面覆盖IC设计、IC验证、嵌入式设计、微电子、半导体制造与工艺、电子电路、EDA工具等。论坛内活跃着大量资深工程师和学生,分享大量实用资料、面试经验、工具脚本和项目讨论,是初学者入门和从业者深造的必访之地。

- 电子工程师论坛:一个更广义的电子技术交流平台,不仅限于IC,还广泛涉及电子电路设计、单片机、电源技术、嵌入式设计、测试测量等。对于解决板级系统集成、模拟电路问题以及嵌入式软件开发非常有帮助。

- 网络工程设计相关社区:虽然与核心IC设计有一定距离,但在涉及网络处理器、通信芯片、高速SerDes等设计时,网络协议和系统架构知识不可或缺。相关论坛有助于拓宽系统视野。

###

从精确描述寄存器行为的SystemRDL语法,到构建复杂验证环境的UVM和SystemVerilog知识,再到从EETOP等专业论坛获取实战经验和最新资讯,构成了IC设计与验证工程师的核心能力图谱。持续学习、积极在社区中参与讨论与分享,是在快速发展的半导体行业中保持竞争力的有效途径。建议工程师们系统性地学习标准语法与验证方法学,同时善用论坛资源,将理论知识与工程实践紧密结合,从而在集成电路的创新浪潮中创造价值。

如若转载,请注明出处:http://www.5288youxi.com/product/26.html

更新时间:2026-04-11 00:43:37