晶振 电子系统的心脏与脉搏——从原理到网络工程设计的全面解析

在电子世界的微观领域,有一类元件虽小巧,却如同心脏之于人体、节拍器之于乐队,为整个系统提供精准稳定的时间基准与运行节律。它,就是晶体振荡器,简称晶振。本文将深入剖析晶振的原理、类型、关键参数,并聚焦于其在现代网络工程设计中的核心应用与选型考量,堪称一份详尽的技术指南。

一、晶振的核心原理与类型

1. 工作原理:压电效应的魔力

晶振的核心是石英晶体片,利用其独特的压电效应:在晶体片两侧施加电场时,晶体会产生机械形变(逆压电效应);反之,对晶体施加机械压力时,其两侧会产生电场(正压电效应)。当交变电压施加于晶体时,它会以特定的固有频率产生机械振动,这个频率极其稳定,仅与晶体的切割方式、几何尺寸有关。晶体与外部电路共同构成一个高Q值的谐振回路,从而输出精准的时钟信号。

2. 主要类型

无源晶体(Crystal): 需要外部电路(如芯片内部的振荡器)才能起振,自身为二端元件。成本较低,但频率精度和稳定性依赖于外部电路设计。

有源晶振(Oscillator): 将晶体、振荡电路、输出驱动电路集成于封装内,直接提供方波或正弦波时钟输出。通常为四端元件(电源、地、输出、有时包含使能端)。具有输出稳定、设计简便、抗干扰能力强等优点,是网络设备中的主流选择。

* 常见封装: 从传统的直插(如HC-49/S)到主流的贴片(如SMD3225、2520、2016),封装小型化是趋势。温补晶振(TCXO)、压控晶振(VCXO)、恒温晶振(OCXO)等则针对更高精度的应用场景。

二、关键性能参数解读

网络设备对时序要求严苛,选择晶振时必须关注以下参数:

- 频率精度与稳定度: 通常以ppm(百万分之一)表示。例如,±10ppm表示在25°C下,频率偏差不超过标称值的十万分之一。网络同步(如IEEE 1588 PTP)需要高稳定度的TCXO或OCXO。

- 工作温度范围: 商业级(0~70°C)、工业级(-40~85°C)、车规级(-40~125°C)。户外或工业环境网络设备需选用工业级以上产品。

- 负载电容与匹配: 对于无源晶体,必须严格按照芯片要求匹配外部负载电容,否则会导致频率偏移甚至不起振。

- 相位噪声与抖动: 衡量时钟信号短期稳定性的关键指标,直接影响高速串行总线(如以太网、PCIe)的误码率。网络交换机和路由器中的高速SerDes对此要求极高。

- 功耗: 对于PoE供电或电池供电的网络设备(如物联网网关、无线AP),晶振的功耗是重要考量。

- 可靠性(MTBF)与抗冲击振动: 确保设备在复杂环境中长期稳定运行。

三、在网络工程设计中的核心应用与选型策略

网络设备高度依赖精确的时钟来协调数据包的发送、接收、路由与交换。

1. 核心应用场景

主系统时钟: 为CPU、FPGA、ASIC等核心处理器提供基准时钟,是整个设备运行的“脉搏”。

高速通信接口时钟: 千兆/万兆以太网PHY芯片、SFP/SFP+光模块、PCIe接口等都需要特定频率的低抖动时钟源,以保证数据链路的完整性。

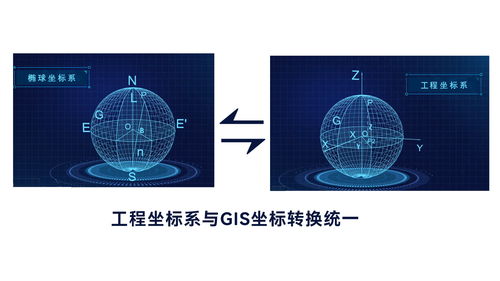

网络同步时钟: 在4G/5G基站回传、SDH/SONET、电信级以太网中,需要超高精度的时钟以实现网络时间同步(如SyncE)或时间同步(如PTP),此时常采用OCXO或高端TCXO。

无线射频时钟: 在Wi-Fi路由器、蜂窝基站中,射频收发器需要非常纯净、低相噪的参考时钟来生成精确的载波频率。

2. 工程设计选型要点

需求分析先行: 明确设备所需的所有时钟频率、精度、抖动要求、接口类型(LVCMOS、LVDS、HCSL等)、工作环境。

优先选用有源晶振: 简化设计,提高系统可靠性,减少PCB布局布线带来的时序问题,尤其对于高速设计。

重视电源与地去耦: 晶振电源引脚必须就近放置高质量的去耦电容(通常为0.1μF和0.01μF并联),并采用星型接地或独立地平面,最大限度隔离数字噪声。

精心的PCB布局:

* 晶振应尽可能靠近其负载芯片的时钟输入引脚。

- 时钟信号线应短、直,避免过孔,并用地线包围进行屏蔽。

- 晶振下方及周围避免布置高速数字信号线,防止耦合干扰。

- 对于无源晶体,负载电容应紧靠晶体引脚放置。

- 考虑冗余与备份: 对于关键通信设备,有时会设计外部时钟输入接口或采用可编程时钟发生器,以接入更高等级的系统参考时钟。

- 供应链与成本: 在满足性能的前提下,选择通用型号、品牌可靠的晶振,保证长期供货与质量稳定。

四、

晶振绝非一个简单的“小零件”,它是奠定电子系统,特别是网络设备稳定、高效、可靠运行的时序基石。从原理理解到参数深究,再到网络工程实践中严谨的选型与精心的电路板级设计,每一个环节都至关重要。随着5G、物联网、工业互联网的发展,对时钟精度的要求只会越来越高。掌握晶振的全面知识,就如同掌握了为数字世界校准脉搏的艺术,是每一位网络硬件工程师不可或缺的核心技能。可以说,在网络工程设计的浩瀚蓝图中,对晶振的深刻理解与妥善应用,是确保信息洪流精准、有序奔腾的关键所在。

如若转载,请注明出处:http://www.5288youxi.com/product/24.html

更新时间:2026-04-07 09:51:00